1. About Me

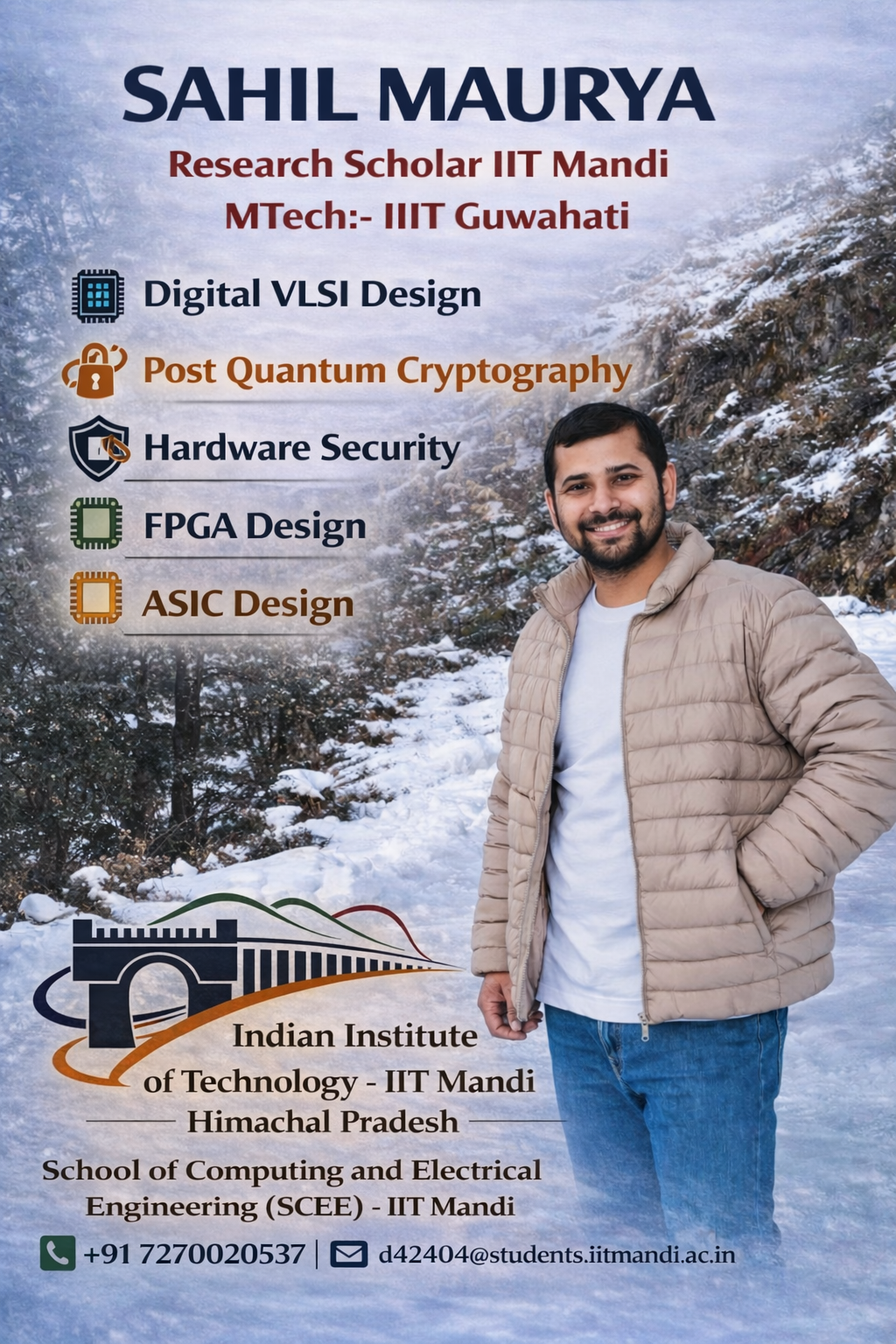

Hello and welcome to my profile! I'm Sahil Maurya, currently a Research Scholar at the School of Computing & Electrical Engineering (SCEE), IIT Mandi. I am a VLSI and Hardware Security researcher, specializing in Post-Quantum Cryptography (PQC) Hardware Acceleration, Secure RISC-V SoC Architectures, Digital VLSI Design, and FPGA/ASIC Implementation.

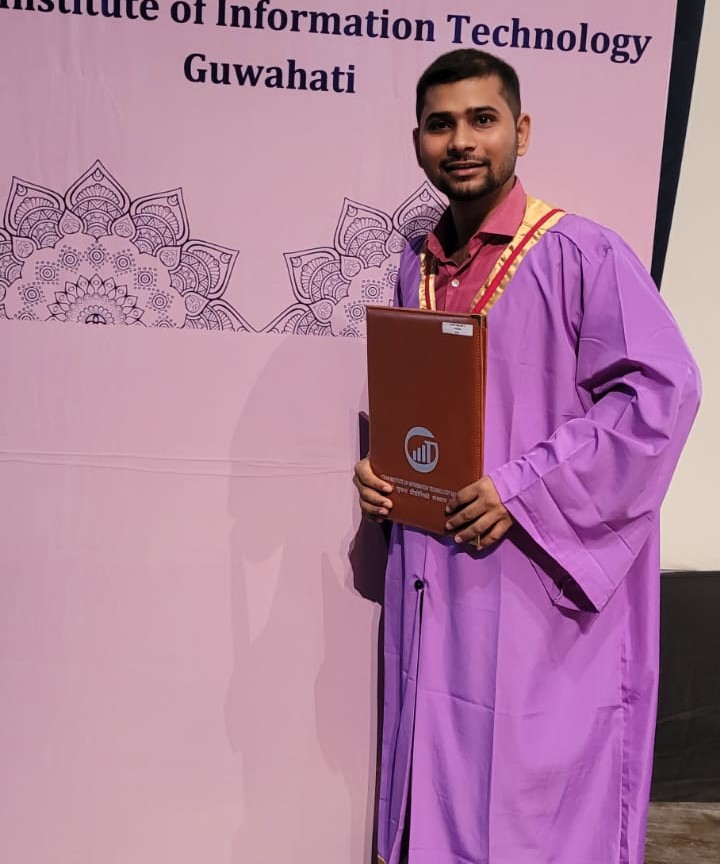

Prior to joining IIT Mandi, I completed my M.Tech in VLSI & Embedded System from IIIT Guwahati with a CGPA of 9.11, securing the 1st Rank. My research focuses on developing quantum-resistant cryptographic accelerators for NIST-standardized algorithms (CRYSTALS-Kyber, Dilithium) with optimized Power, Performance, and Area (PPA).

2. Contact Information

📞 +91-7270020537

📧 d24204@students.iitmandi.ac.in (IIT Mandi)

📧 sahil.maurya21@iiitg.ac.in

🏠 Janki Vihar Colony, Jankipuram, Lucknow, Uttar Pradesh - 226021

🏛️ Current: IIT Mandi, Kamand Campus, Mandi, Himachal Pradesh - 175075

3. Education

- IIT Mandi - Research Scholar (Ph.D.) at SCEE Department (2025 - Present) | CGPA: 8.33/10.0

- IIIT Guwahati - M.TECH VLSI & Embedded System (May 2023) | CGPA: 9.11 - Gold Medalist

- University of Lucknow - B.TECH Electronics & Communication Engineering (2021) | 66.1%

- UP Board - Higher Secondary (2016) | 85% | Secondary (2014) | 85%

4. Publications

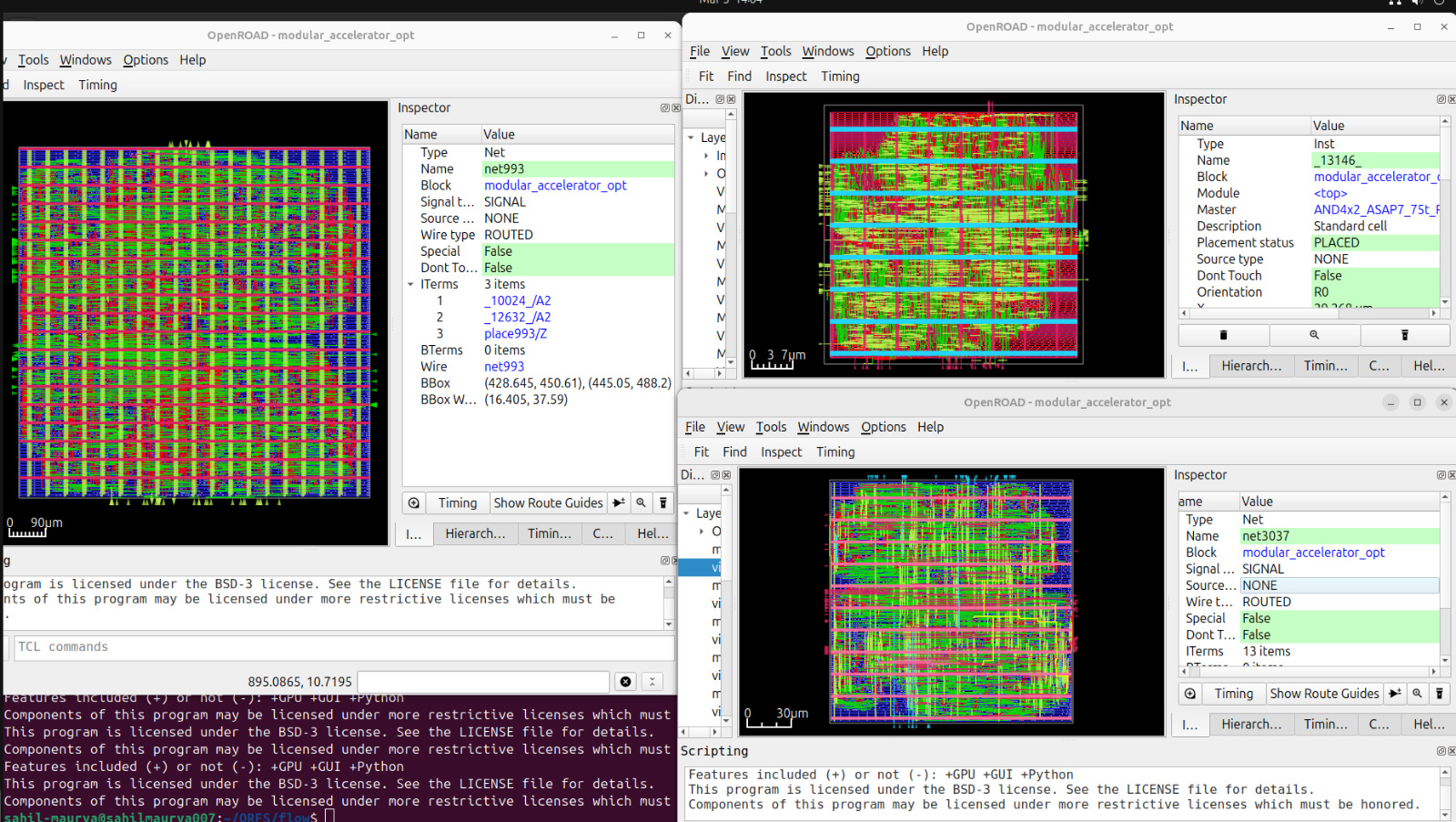

5. Research Projects

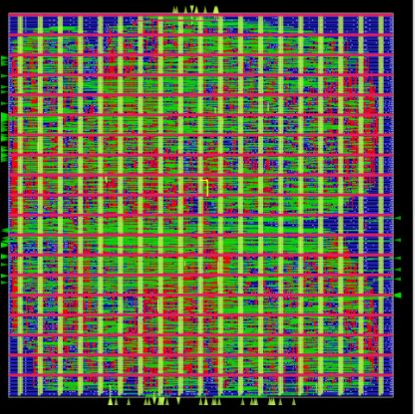

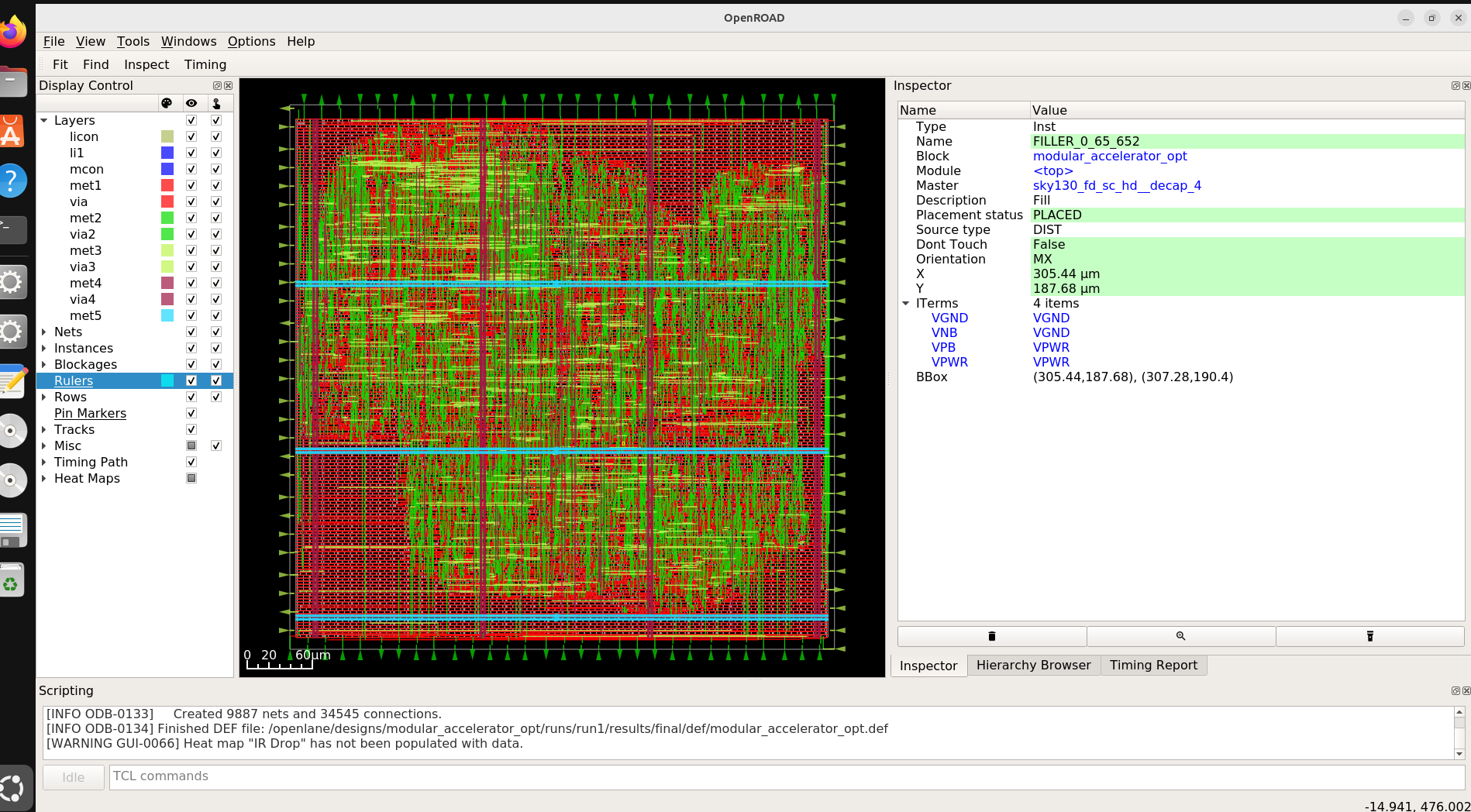

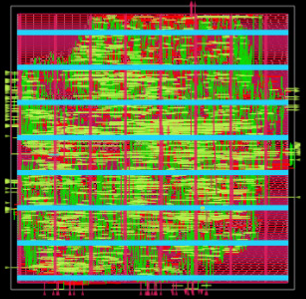

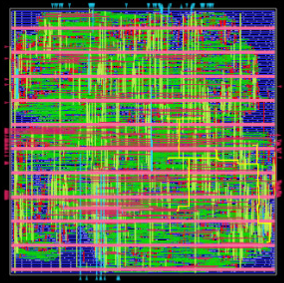

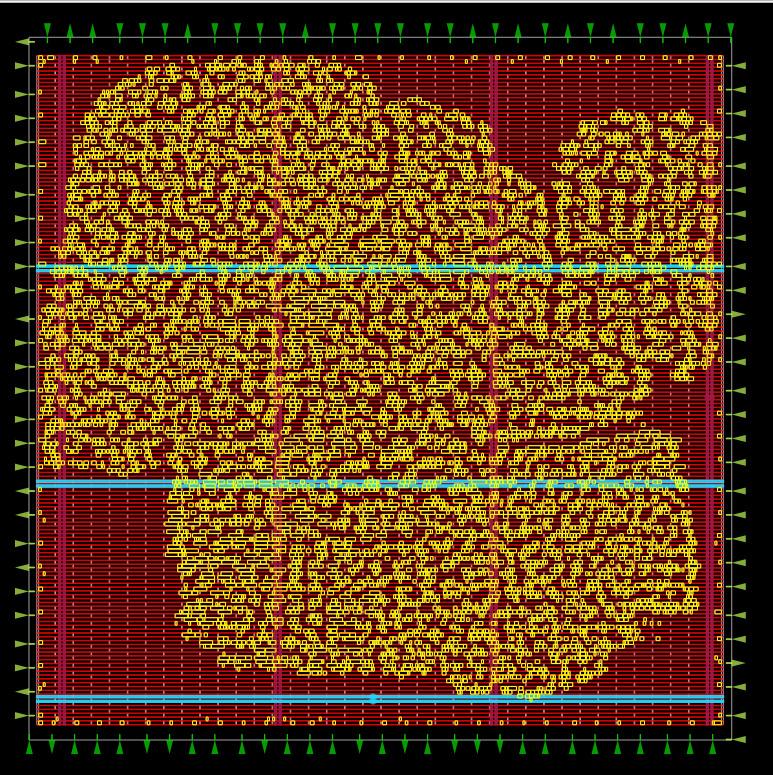

- CRYSTALS-Kyber NTT Hardware Accelerator - High-throughput, side-channel resistant NTT architecture (245 MHz, 1.28 Gbps)

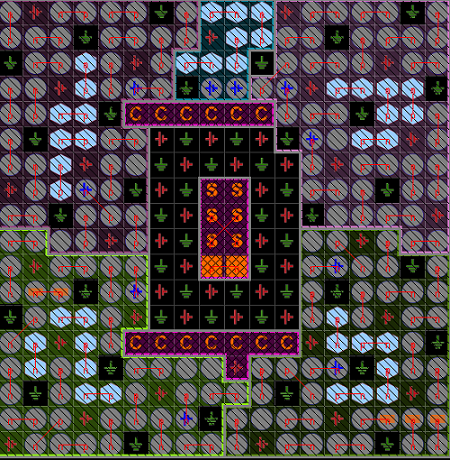

- Approximate Modular Multiplier for R-LWE - 34% area reduction, 33% power savings [IEEE SILCON 2024]

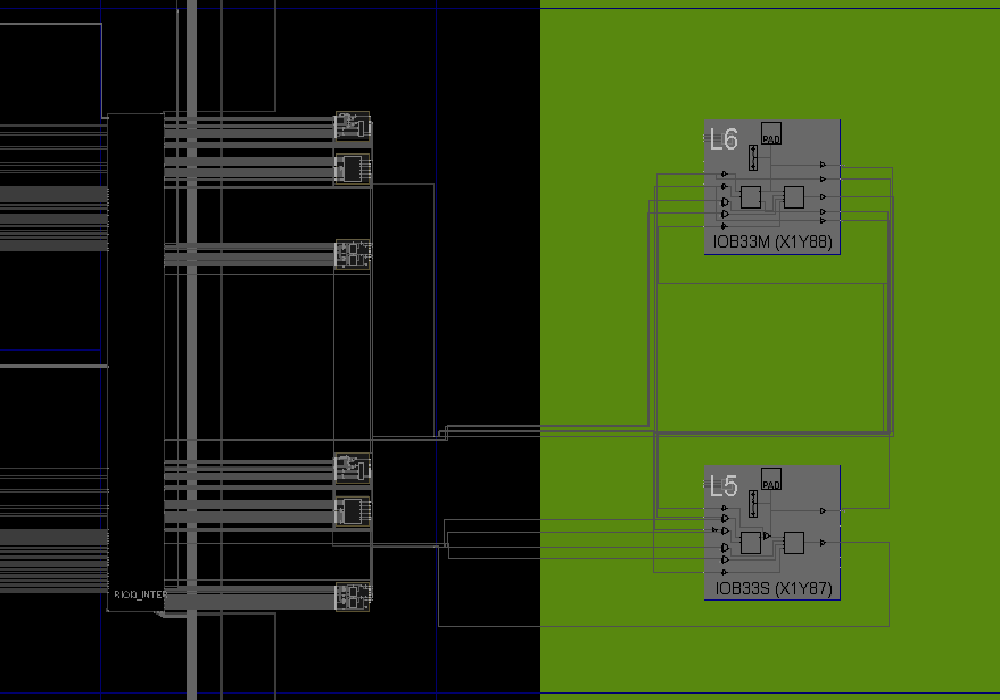

- Toom-Cook Multipliers for Cryptosystem - 32-bit Toom-Cook 2.5 and 3 implementations on FPGA

- IoT Weather Monitoring System - Arduino UNO based system with cloud integration

6. Technical Skills

Languages: Verilog HDL, SystemVerilog, VHDL, Python, C, RISC-V Assembly, TCL

EDA Tools: Xilinx Vivado, Cadence Genus/Innovus, OpenLane/OpenROAD, ModelSim, Intel Quartus

Research Domains: Post-Quantum Cryptography (Kyber/Dilithium), RISC-V SoC, Digital VLSI, Side-Channel Analysis, Hardware Security

7. Relevant Coursework

- Post Quantum Security

- Low Power VLSI

- VLSI Circuits and System

- Architectural Design of Digital ICs

- Reconfigurable Computing

- System Modelling Lab

- VLSI CAD Lab

- Digital VLSI Design

8. Certifications

- System Design Using Verilog HDL - Udemy (2022)

- VSD Static Timing Analysis Parts 1 & 2 - Udemy (2025)

- Python for Data Science, AI & Development - Coursera (2023)

- Cadence RTL to GDS Flow - Entuple Technology (2024)

- VLSI Design Flow using Vivado - CoreEL/Xilinx (2024)

9. Achievements & Awards

- 🏅 Gold Medalist - Highest CGPA (9.11) in M.Tech ECE, IIIT Guwahati

- 🎯 IIT Mandi Research Scholar - SCEE Department (2025-Present)

- 📚 IEEE HiPC 2025 & IEEE SILCON 2024 Publications

- ⭐ Best Paper Nominee - IEEE SILCON 2024

- ✍️ 2nd Prize - Creative Writing competition, EN-LIT Lucknow University

🔬 Chip Design Gallery (ASIC / FPGA)

📌 References

- Dr. Babita Jajodia - M.Tech Supervisor, Assistant Professor at IIIT Guwahati

- Dr. Rakesh Biswas - M.Tech Thesis Panelist, IIIT Guwahati

- Dr. Siddharth Singh - B.Tech Supervisor, HOD at Lucknow University

© 2025 Sahil Maurya | IIT Mandi Research Scholar | Hardware Security & Post-Quantum Cryptography

Last Updated: March 2026